## INVESTIGATING PACKAGE BACKSIDE SOLDER BUMPS INDUCED POST BURN-IN

Obed, Rommel Jr. S.<sup>1</sup>

Limbaga, Krizelle P.<sup>2</sup>

Patalen Julius Albert C.<sup>3</sup>

Materials Engineering – Quality Department<sup>1,2,3</sup>

Ampleon Manufacturing Philippines Inc.

rommel.obed@ampleon.com<sup>1</sup>; krizelle.limbaga@ampleon.com<sup>2</sup>; julius.patalen@ampleon.com<sup>3</sup>

### ABSTRACT

Defective samples were detected to form backside bumps post burn-in. It was observed that the bumps all form on the bottom short side with respect to the burn-in loading board.

The study utilized Ishikawa analysis then focused on the possible causes related to machine and material factors where analysis focused on the melting of tin and its orientation on the loading board.

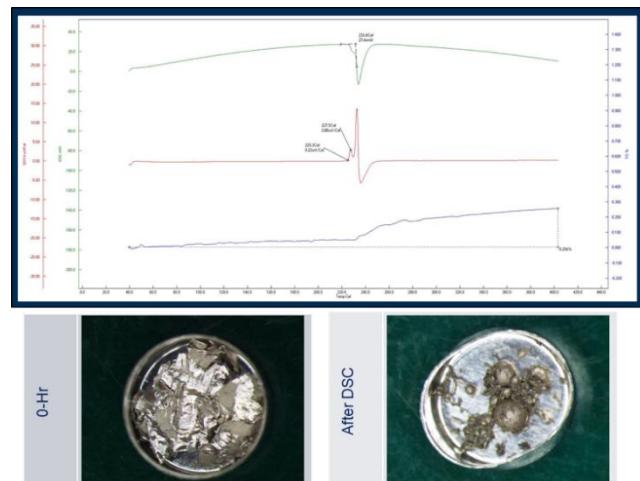

Differential scanning calorimetry confirmed that the tin backside plating melts at 231.6 °C the theoretical melting point of pure tin. This was used to note the thermal behavior of tin on the backside is ideal.

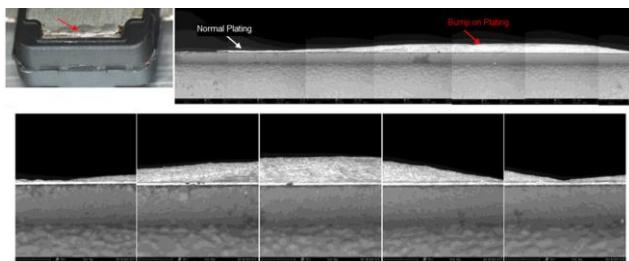

Mechanical sections revealed dense, non-blister defects, supporting the hypothesis from the Ishikawa analysis. The study then focused on investigating the possibility of tin potentially de-wetting from the copper. A heating setup using a hotplate and an enclosure was used to confirm the de-wetting. This was done to effectively heat the samples quickly in short time periods.

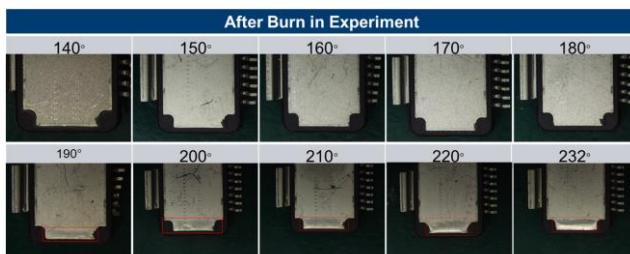

The study was able to replicate the failure on the defective samples. At 190°C, bumps formed similar to the defect sample. Exposure to elevated temperatures cause the plating on the backside to flow downwards, then concentrating on the bottom part to form the bump. This has successfully replicated the failure mode encountered by the initial occurrence of the issue.

### 1. 0 INTRODUCTION

The focus of the study is to determine the root cause of an encountered backside over-molded package found post burn-in. Several hypothesis can contribute to such a defect which include unclean substrates,, impure materials, remelt or de-wetting.

#### 1.1 Tin Plating Defects

Plating with tin is an established, effective and cost-effective way of plating semiconductors. Tin is relatively inert and provides effective corrosion resistance to copper. Copper provides numerous advantages for semiconductor performance due to its conductivity and formability.

##### 1.1.1 Common Tin Plating Defects

Semiconductor manufacturing is a delicate process since it often requires high controls in terms of cleanliness and procedures. This applies not just in the manufacturing aspect but also the condition of the raw materials.

For a copper surface to be effectively plated by tin, it must be prepared accordingly, making sure that the metal is pre-treated, commonly by etching processes and then thoroughly cleaned.

Focusing on the cleanliness of the copper pre-plating, ineffective cleaning can cause adhesion issues in the plating, dull coloration, blistering, pitting and unevenness in the plating.

These are all common assumptions when encountering defects in tin plating.

##### 1.2 Burn-in in Semiconductor Manufacturing

More Ampleon customers are now requiring burn in. This is done by inducing accelerated test conditions like elevated voltages and temperatures to the devices under test.

These elevated conditions are necessary in burn-in to hasten the processing time. Production UPH (unit per hour) is still key to optimizing process flow.

##### 1.2.1 Limitations of Burn-in

The negative implications of these elevated parameters, particularly parameters that induce thermal stress like heat and electrical voltage, are that these are not real-world

conditions as these are accelerated conditions. Most accelerated testing conditions are like this, where the increased parameters minimize the cycle time of tests but at the expense of exposing the samples to unrealistic stimulus that is not applicable in typical service conditions.

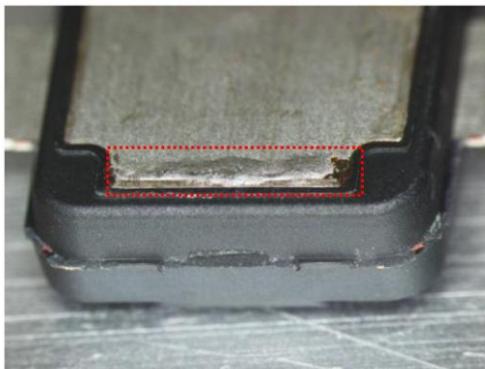

This could introduce defects that are not ideal on real-world applications. The defect seen below on Fig 1.1 shows that there is a bump seen concentrated on one of the short sides of the package. Investigating what caused the formation of this defect during burn-in is the objective of this study.

Fig 1.1 The defective sample showing unevenness on the tin plating on the backside. This was observed post-burn in.

## 2. 0 REVIEW OF RELATED WORK

Ampleon over-molded packages typically consist of C19210 copper lead frames molded with epoxy molding compound and then plated with 99.99% tin.

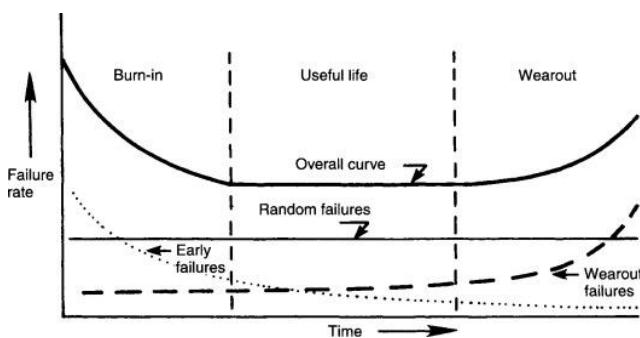

According to the definition of Advanced Energy, the necessity of burn-in is to provide early detection of devices that constitute early-life failures<sup>2</sup>.

Fig 2.1 A reliability/ bathtub curve<sup>1</sup>

Burn-in induces high temperatures on the tested devices. This includes excessive compressive stress and elevated temperatures.

Uneven plating also can be caused by de-wetting. De-wetting is a phenomenon where tin tightens and reduces its surface tension. This has been observed in previous studies where improper handling under elevated temperatures can cause de-wetting<sup>3</sup>.

Tin de-wetting through reflow is a risk already commonly controlled with proper precaution. Burn-in has continually increased adaptation in semiconductor manufacturing and tin de-wetting in burn-in is a phenomena this study aims to provide more information on.

## 3.0 METHODOLOGY

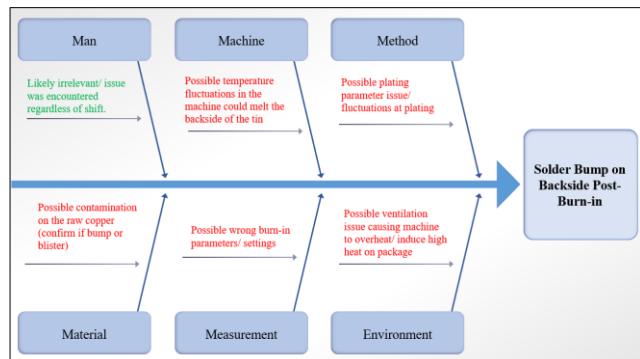

Upon encountering this issue, Defining the problem description was done using Ishikawa analysis. It was defined that the likely sources of the defect are machine (temperature fluctuation), method (plating process parameter defect), material (raw copper material defects), measurement (burn-in parameters) and environment (ventilation issues).

Fig 3.1 Ishikawa analysis done by the team for bump on backside issue.

The technical team looked further into the machine and material factors while support groups investigated methods, measurement and environmental factors.

### 3.1 Material characterization

Initial characterization was first done via differential scanning calorimetry (DSC). This was done to check the melting point of the tin plating being analyzed. The tin plating was scraped off samples for this test.

### 3.2 Failure analysis of the initial sample

Failure analysis was done through mechanical cross-section to effectively define the nature of the backside anomaly of the package. This was done through mechanical cross-section

through silicon carbide (SiC) sandpapers and an automatic grinding wheel.

### 3.3 Heat simulation on experimental samples

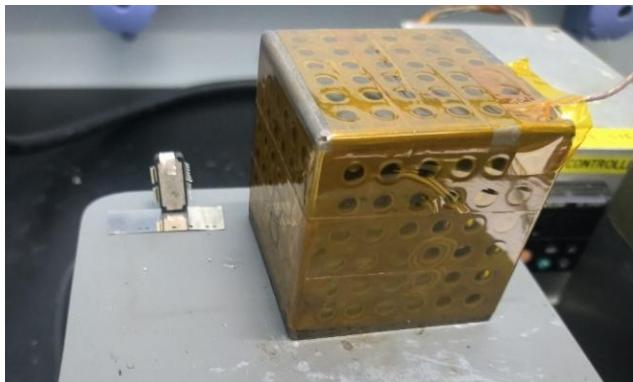

The factor identified to induce the defect was excessive temperature exposure of the unit while in burn-in. At the time of analysis. The most practical way to do this was to heat the samples on a sideways orientation. This follows how the units are oriented on the burn-in boards (see Fig 3.3).

The study required heat application to the samples in an effective way while on a short time and at multiple different time intervals. Additionally, to prevent production line disturbance, the team decided to use a setup consisting of a hot plate and cube-shaped enclosure covered with poly-imide tape. A thermocouple inside this enclosure measured the temperature. The package was then placed on an improvised metal holder inside the enclosure while the heat was turned on (see Fig 3.2). The thermocouple was attached positioned near the sample experimental sample itself to better reflect the thermal state of the sample.

Fig 3.2 Improvised heating setup to induce the bump defect.

In the methodology done in the study, it was first made sure that the temperature was stable through the thermocouple before units were placed inside the enclosure. The samples were left inside for 20 seconds before being removed. Visual inspection was done to inspect if the failure mode was replicated in the samples. This was done from 140 Celsius up to the max melting point of tin at 232 °C, in 10-degree increments. Three samples, heated in succession, were used per temperature setting.

The samples are in an upright position, as seen on Fig 3.2, due to the orientation of the affected samples as they are loaded on the board. This can be seen on Fig3.3 below.

Fig 3.3 Sample burn-in load board

## 4.0 RESULTS AND DISCUSSION

The first action was to investigate the various identified factors on the Ishikawa diagram.

From the analysis, a check on the processing history and work instruction shows conformance to released parameters and checking on the working environment showed that the burn-in machines have proper ventilation and are functioning optimally.

Fig 4.1 Differential scanning calorimetry curve (DSC) for the post plated tin.

For the material aspect validation. The first action was to characterize the melting point of post-plated tin via DSC. This will guide the investigation on what is the temperature limit that the tin is susceptible to deformation. The DSC (see Fig 4.1) indicated that the melting point of the plated tin is 231.6 °C. This is close to the theoretical value of pure tin. It is also noteworthy that 231.6 Celsius is a low temperature in terms of semiconductor manufacturing.

The defective sample underwent a mechanical cross section to look inside the bump on the backside. It was found to be dense and not hollow, meaning it is not a blister. This led the team to consider possible uneven plating or de-wetting due to hot temperatures.

Fig 4.2 Mechanical cross-section results done on the defect unit showing a dense bump.

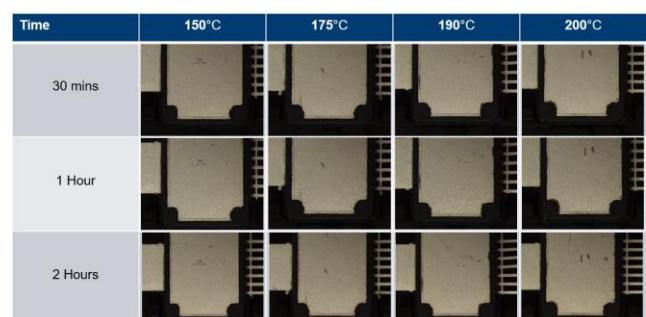

To investigate de-wetting, using the cube enclosure and hotplate setup on Fig 3.2, samples were loaded for 20 seconds for each temperature configuration. As seen below on Fig 4.3, no bumps were generated at temperatures up to 180 degrees. Bumps started appearing at 190 degrees onwards with the bump size increasing with higher temperatures. The amount of solder concentration at the bottom side increased as the temperature increased. This indicates that the amount solder deposition towards the bottom of the package increased. This formation aligns with tin deposit formations seen on the study from Kurtz et al.

This setup was able to replicate the defect seen on the burn-in load boards exactly.

Fig 4.3 Results of the heating experiment done on the heating setup. As shown, the bumps were induced with increasing temperature.

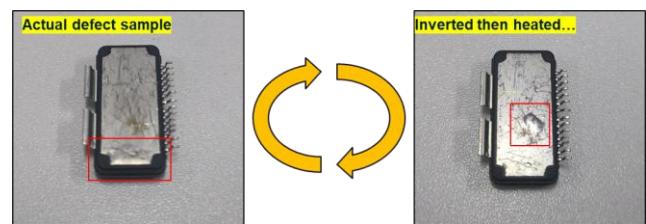

Upon replicating the defect, validation was done using the first defective unit. The sample underwent the same heat exposure at 232 °C but the bottom side with the bump is put on top. After the experiment on the actual defect sample, the solder bump moved downward which means that the defect was able to flow down at elevated temperatures.

Fig 4.4 The defect sample underwent the same heat exposure as the experimental samples.

This bump formation on a lower temperature compared to the melting point may indicate the heating setup has a higher temperature than the thermocouple measured. Validation and production derisking were further conducted.

Using in-line settings on ovens, the max temperature used in Ampleon regardless of package is 200 °C. Samples placed upright (same orientation as the burn-in board) were placed in ovens to check if the tin will also de-wet. No de-wetting was observed as seen below on Fig 4.5, indicating no risk of de-wetting in ovens.

Fig 4.5 Samples that underwent over heating while placed in upright position.

## 5.0 CONCLUSION

The encountered bump on the backside is concluded as de-wetting of the tin on the backside of the affected samples.

This is due to several factors like:

- The defect is not a blister which does not point to contaminated substrate or plating chemical.

- Successfully replicating the failure mode through the application of direct heat to the sample in an upright position.

This study showed how the low melting temperature of tin can induce defects like bumps, especially on hot temperature tests. The root cause is caused by the melting of tin due to hot temperatures induced by the burn-in process.

## 6.0 RECOMMENDATIONS

# 34<sup>th</sup> ASEMEP National Technical Symposium

This study will be informative especially in other hot temperature applications like reflow and reliability processes like temperature cycling (TC) and high temperature storage life (HTSL).

Another action can be to inform the tin plating department if further actions can be done to control the remelt of the tin plating. Changing parameters or plating chemical additives could possibly be influential to control remelt.

## 7.0 ACKNOWLEDGMENT

The authors would like to thank the following for their support of this study:

- Mario De Vaan – Sr. Director, Quality & Reliability, Ampleon Phils., Inc.

- Manolito Maalat – Sr. Manager, Failure Analysis/ Reliability and Calibration, Ampleon Phils., Inc.

## 8.0 REFERENCES

1. David J. Smith, "Reliability, Maintainability and Risk (Seventh Edition), Butterworth-Heinemann, 2005

2. "Burn-in" Advanced Energy. 2025 <https://www.advancedenergy.com/en-us/applications/industrial/analytical-test-and-measurement/burn-in/>

3. Kurtz, Olaf & Barthelmes, J. & Rüther, Robert & Kühlkamp, P. & Moniak, A.. (2013). Re-melting behavior of tin coatings. Galvanotechnik. 104. 276-287.

## 9.0 ABOUT THE AUTHORS

Rommel S. Obed Jr. is a graduate of BS Materials Engineering from the University of the Philippines - Diliman. He is a Senior Materials Quality Engineer currently at Ampleon Philippines, Inc where he handles BOM material qualifications and material cost saving initiatives.. He is a product of the Ampleon Cadet Engineering (ACE) program. He specializes on die attach

technologies like 80Au20Sn, Silver sinter, Pb soft solder. He also specializes in substrate surface level material analysis.

Krizelle Limbaga is a Failure Analysis Engineer in Ampleon. She started her career in Cypress Mfg. Ltd. in 2011 as Autoline Manufacturing Technologist until becoming a Failure Analysis Engineer in 2014. She later joined Ampleon Philippines in 2023.

Throughout her experience in the industry, she gained valuable knowledge on die attach and wirebond assembly process, product reliability, and physical failure analysis of different semiconductor packages and technologies.

Julius Albert C. Patalen is a Senior Materials Engineering Technician in Ampleon. He started his career in NXP Semiconductors Philippines in 2013 as a Test Operator until becoming an Outgoing Quality Inspector. He carried over his role as inspector upon Ampleon's divestment from NXP and joined the Materials Engineering group in 2020. Throughout his experience in the industry, he gained valuable knowledge on product-level testing, product reliability, material-level risk assessment and material characterization.