## High Speed Dicing Application for Narrow Saw Street SiC Wafers by Full Cut Process

Eli Q. Novenario, Rex T. Dao Ayan, Rodel Palad

Pre-Assembly Department, Ampleon Philippines Inc.

### Abstract

Silicon carbide wafers (SiC) offers wide range of RF Power application because of its ability to operate at higher voltage, temperature, higher power densities and wider frequency bands compared to standard silicon-based wafers, that is why Semiconductor industry is considering conversion to this technology. But SiC material is posing significant challenge to Wafer Sawing Process since it is the third hardest compound next to boron carbide and diamond. Being so high on the hardness index, dicing using the conventional diamond blades employ dual pass dicing at slower speed to control stresses up and since the material is also brittle, chipping is also a common problem limiting its yield and thruput time.

The objective of this study is to define a full cut dicing solution that will reduce the high sawing thruput time of SiC wafers.

This paper discussed the detailed approach on how full cut or single pass dicing can be applied to narrow street width SiC wafers with high yielding performance thus ensuring the production efficiency and quality of the final product.

Results showed that following the structural approach of tool selection, single-pass dicing at double the conventional speed is enabled maintaining high yield and ensuring sufficient Defect-Free Zone (DFZ) clearance. This approach reduced the production throughput time by 50% while maintaining the die quality and dimensional integrity.

### 1. 0 INTRODUCTION

Mechanical blade dicing principle follows the rule of thumb of “hard to soft or soft to hard” meaning, a relatively harder tool is used in singulating softer work piece or vice versa. SiC wafers being hard material require softer bonder tool by standard dicing principles. But this combination situates the process and tooling set up to some application restrictions. Resinoid type blades have inherent limitations to thinner dimensions, being a soft bonder material. This tool requirement

limits the SiC wafer sawing lane width to a minimum of 80 um, leaving no provisions to improve the die densities (number of dies per wafer) for future design improvements.

Resinoid blades are effective in dicing conventional silicon, they lack the durability and cutting power required for harder materials (SiC). The reason why this blade is operated at reduced feed rates, about 83% slower than standard sawing speed resulting to lower thruput time. Given this present industry solution, SiC dicing remains to be an issue for mass production entailing a structural approach to resolve the following technological problems.

1. Blade glazing and loading – a tooling condition when the blade suddenly reduces its cutting power due premature grit fracturing or contamination build covering blade's cutting tip with scrapes or dicing contaminants.

2. Limitation in the availability of usable dicing blades to larger grit sizes. SiC needs bigger abrasives for its high cutting power requirement, this also sets restriction for the inclusion of PCMs and backside metallization layers to the wafer.

3. The blade thickness which dictates the kerf width should not be less than 50 microns for higher grit concentration exposed on its cutting tip, this resulted to lower die quantity per wafer since more than 80 microns of the SiC material is allocated just for the sawing lane alone.

4. Sawing process is operating at relatively higher load, sudden interruption of cooling supply creates a hot spot along the dicing contact which potentially can trigger stress raisers leading to cracks and chipped outs.

Given the above challenges for dicing SiC based material, the structural solution is preventing the scrapes contamination on abrasives and keeping the cooling passage open by designing a dicing blade with self-sharpening property but maintain its stiffness to allow higher thickness to protrusion index.

This study aims to develop a high-speed, full-cut dicing process using a self-sharpening blade matrix suitable for narrow- street SiC wafers”

## 1.1 SiC Wafer Construction Analysis :

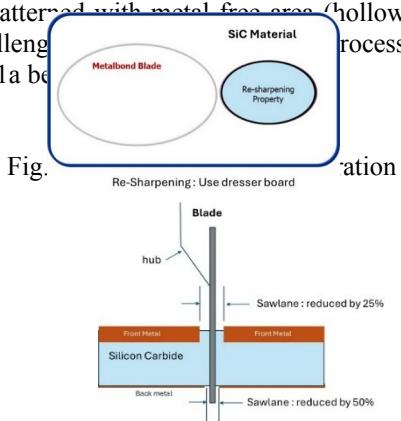

By wafer design, the sawing lane (street width) of the wafer was reduced by 25% and 50% top and backside respectively to maximize the die density. The back part is patterned with metal free area (hollow) which also a challenge in the process, illustrated in fig.1a below.

Mechanical dicing for this wafer technology will require the thinnest possible blade to allow kerf clearance hitting the first active layer of the die.

## 1.2 SiC Wafer Dicing Characteristics :

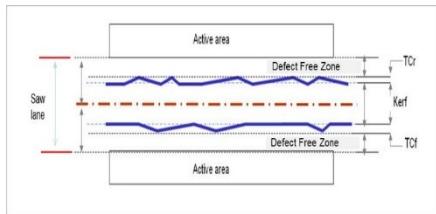

The critical quality characteristic of this material that will be in consideration to this study is the Defect Free Zone (DFZ), it is defined as the clearance of the kerf edge to the first active layer of the die, see illustration below.

Fig. 1b : Defect Free Zone (DFZ)

Top chip (TCr and TCr) is the cut deviation from the kerfline, while kerf width is the blade impression without the chipping. The cut width or kerf and chip size are direct functions of the blade thickness and grit size, therefore the selection of these blade parameters are key factors with direct impact to DFZ requirement.

## 1.3 Blade Bonder Selection :

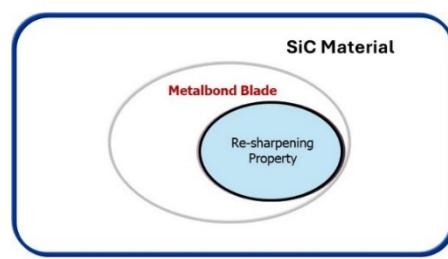

Since the sawing lane width was reduced by design, resinoid type bonder is not applicable for this case because of its thickness to protrusion limitation (soft bonder material stiffness limitation). Metalbond hub type blades offer rigidity against higher exposure but

with reduced re-sharpening property. The solution is to define a blade matrix which uses SiC material as dressing medium.

Fig. 1d : Metal Blade Sharpening Diagram

The re-sharpening property is not incorporated in the metal bond blade, it uses an offline dresser board (or pre-cut board) to remove saw adherents and expose the grits after several cut intervals.

But considering SiC material as a dressing medium itself, this could result in self-sharpening sawing process, and changes the context of the operation.

Fig. 1e : Metal Blade Self-Sharpening Diagram

The above figure illustrates the built-in property of the blade to re-sharpen and keep the sawing load stable during cutting.

## 1.4 Blade Matrix Selection :

The main blade factors into considerations are blade for SiC dicing are bonder types, abrasive (grit) size and concentration, tool thickness to ensure that kerf plus chipping will not extend up to the active part of the die.

Tab. 1a : Blade Selection Guide for SiC Wafer

| Process Parameter      | SiC Dicing Solution | Remarks                                         |

|------------------------|---------------------|-------------------------------------------------|

| Abrasive concentration | Low                 | Wider chip pocket to maximize grit's efficiency |

| Abrasive size          | Coarse grit         | Large grit ( consider reduced saw lane)         |

| Bond type              | Hard bond           | Hard Bond for SiC Material                      |

| Blade thickness        | Thin                | Kerf to Wafer thickness ratio                   |

| RPM                    | High RPM            | Higher dicing power for SiC application         |

| Feed rate              | Higher than control | Self dressing                                   |

| Cut height             | Full cut            | Attain self sharpening/ saw efficiency          |

Blade speed (RPM) was pre-defined based on the dicing rule of thumb where the tool was made relatively harder vs. the SiC workpiece by increasing grit's rotational speed (RPM) at the same time there comes a re-sharpening point where SiC becomes a dressing medium by full cut engagement at higher feed rate.

In full cut stroke, the grit function is to completely dice the workpiece and compensate the harmful effects of material displacement while the bonder should be strong enough to hold the grits (in full load) during the cut engagement, thus attaining efficient and self-sharpening sawing process.

## 2. 0 REVIEW OF RELATED WORK

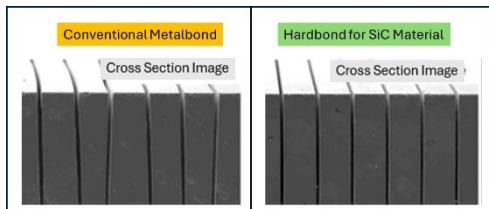

Reference to SiC material dicing application in the industry, the stiffer metalbond is recommended based on its cut cross section at full cut engagement. See fig. 2a below.

Fig 2a : Full Cut Cross Section

Metalbond blade type for SiC was pre-selected from different tool suppliers in the industry.

Other researchers have investigated the use of metal-bonded blades for SiC wafer dicing. These tools offer better wear resistance and can handle larger abrasives, but often suffer from issues like blade glazing, where accumulated debris interferes with the blade's cutting ability, causing fluctuations in cutting force and increasing the risk of mechanical defects. In parallel, single-pass or full-cut dicing methods have gained traction to streamline the process and eliminate multiple

cutting depths (step cut). It was also demonstrated that with precise control of blade parameters, such as thickness, grit concentration, and spindle speed full-cut processing can achieve reliable results on SiC wafers with narrow street designs. Success in these applications depends on achieving a balance between tool rigidity and effective chip.

## 3.0 METHODOLOGY

Given the blade selection guidelines from the previous sections blade formulation matrix was defined – coarse grit, low concentration and relatively thinner to attain DFZ requirement. Three blade types were prepared for comparative test cutting.

- Blade A : From Supplier 1, hard-metalbond type

- Blade B : From Supplier 2, hard-metalbond type

- Blade C : Control, resinoid bonder type.

### 3.1 Experimentation Methodology

The high-level planning diagram below describes the framework of experimental methodology.

The blade formulation matrix is also based on industry manufacturability standards, making sure that there will be no additional cost involved on tool customization at supplier's side.

The maximum blade RPM setting was based on the kerf to exposure (K/E) ratio table provided by tool manufacturer and the technical mechanical capability of the equipment rigidity to maintain stable vibrations at higher spindle RPM settings.

Zero-hour Preliminary Statistical Study (PSS) includes comparative analysis on top and back chipping, kerf and descriptive analysis on kerf finish morphology (sidewall crack raiser check).

Tab. 3a : Evaluation Table

| Run # | Description            | Blade Type                 | Grit Size/Concentration | Feed rate | RPM/Cut height |

|-------|------------------------|----------------------------|-------------------------|-----------|----------------|

| 1     | Single pass - Full cut | <b>Blade A</b> : Metalbond | Coarse/ Low             | 8mm/s     | High/Sawnthru  |

| 2     | Single pass - Full cut | <b>Blade B</b> : Metalbond | Coarse/ Low             | 8mm/s     | High/Sawnthru  |

| 3     | Double pass            | <b>Control</b> : Resinoid  | Medium                  | 5mm/s     | Medium/60/40   |

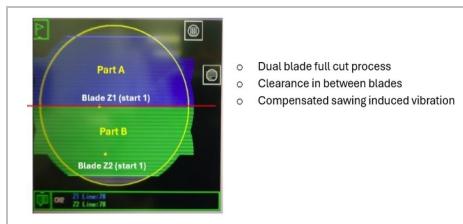

Since the sawing equipment is dual spindle and both will be used to full cut, Blade # 1 (Blade Z1) was set to cut starting at the mid- position to divide the wafer into two parts to control the sawing vibration coming from the two spindles- Blade Z1 for Part A and Blade Z2 for Part B.

Fig 3a : Dicing Direction

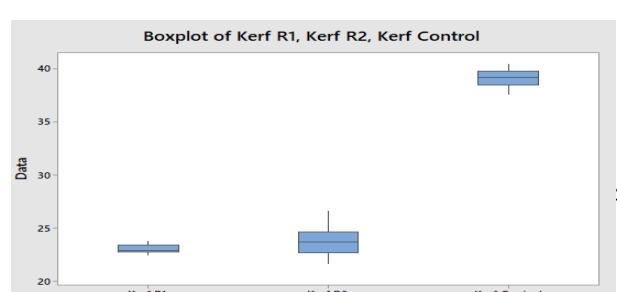

Kerf performance is acceptable for all runs based on tool specifications of  $\pm 5 \mu\text{m}$  tolerance from the blade thickness.

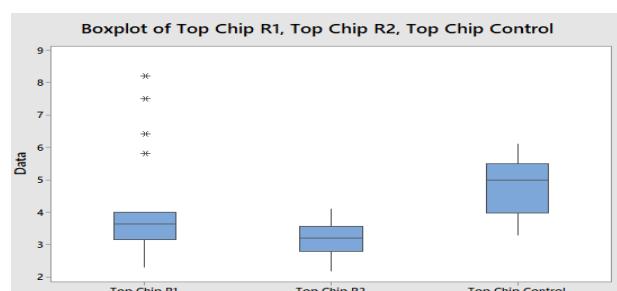

Combining the box plots in Figures 4a and 4b, the top chipping and kerf width distribution across multiple blade trials, Run #2 exhibited the least variation in top chipping and maintained kerf widths well within the  $\pm 5 \mu\text{m}$  specification limit, indicating stable blade engagement. The reduced chip scatter supports improved cut consistency under full-cut conditions.

## 4.2 Defect Free Zone Analysis

The estimated Defect Free Zone was computed taking the baseline saw lane width design of 60um. The higher DFZ value means bigger chip clearance from the first active layer of the die (the higher the DFZ the better)

Tab 4a : Estimated Defect Free Zone Analysis

| Run     | Max Kerf | Max Top Chip | Estimated DFZ |

|---------|----------|--------------|---------------|

| 1       | 23.8     | 8.2          | 14            |

| 2       | 26.6     | 4.1          | 14.65         |

| Control | 20.4     | 6.1          | 16.75         |

on Top and Kerf

Top chip plot comparison showed relatively controlled cut deviations results from run # 2.

Fig. 4a : Top Chip Box Plot

\*all measurements are in microns ( $\mu\text{m}$ )

\*DFZ=(sawlane - (max kerf +max chip))/2

For this specific measurable requirement, run # 2 is better than other runs.

## 4.3 Cut Finish Morphology Results

Cut finish (Cut cross section) showed minimal backside metal displacement, but signs of sawing stress raisers were seen on runs 1 and 3 manifested by triangular chipping and grit rubbing effect respectively.

Tab 4b : Morphology Analysis

| Run     | Side Wall Photo | Remarks                                       |

|---------|-----------------|-----------------------------------------------|

| 1       |                 | with triangular chip                          |

| 2       |                 | No triangular chip                            |

| Control |                 | No triangular chip. With sign of grit rubbing |

Stress raisers (on runs 1 and 3) just showed the need for blade re-dressing, therefore re-sharpening objective was not met on these set up.

### 4.5 Summary Analysis

Summarizing the results in terms of quality and productivity requirements, run # 2 is the preferred blade and process set up to attain self-dressing saw process with twice the speed of existing/ released process.

Tab 4c : Results Summary Table

Die strength measurements comparing the samples from mechanical blade dicing vs. stealth dicing.

### 7.0 ACKNOWLEDGMENT

The Authors would like to thank Senen Lachica –Wafer Test and PRE-ASSEMBLY Director, Toss Villamil – AMP Sr. Director for Manufacturing and Neilo Bandelaria – AMP General Manager for their guidance and support on this project.

| Special thanks to                                       | Top Chip             | Kerf   | DFZ            | Morphology         | Saw Productivity                     |

|---------------------------------------------------------|----------------------|--------|----------------|--------------------|--------------------------------------|

| New Technology in wafer structure of full cut tools and | Acceptable chip size | Passed | Acceptable DFZ | With stress raiser | 2x faster than control (Single Pass) |

| Control                                                 | Smallest chip size   | Passed | Highest DFZ    | No stress raiser   | 2x faster than control (Single Pass) |

|                                                         | Acceptable chip size | Passed | Acceptable DFZ | With stress raiser | Reference (2 pass)                   |

Special mention to our blade technical application support (blade manufacturer and local sales) for providing blade and dresser board samples during the evaluation process.

### 5.0 CONCLUSION

The combination of coarse grit, low concentration, metal bond material blade and full cut process situates the dicing process to the following conditions.

- Efficient dicing process, coarse grit at low concentration increases the “chip pocket” where each grit shares proportionate load during engagement (individual grit is cutting instead of polishing).

- The full cutting engagement of the blade, and the inherent hardness property of SiC wafer situates the tool to a self-sharpening condition (blade maintains its sharpness), thus feed rate can be increased resulted in faster dicing.

- Metal bonded blade is a stiff material, therefore can be constructed relatively thin, applicable for narrow sawlane SiC wafer.

From the preliminary statistical analysis and morphology inspection, Run #2 fulfilled both quality and productivity requirements, validating it as the most suitable tool and process setup for next-generation SiC wafer dicing application

### 6.0 RECOMMENDATIONS

Qualification of run # 2 process to release for full production

Software upgrade of Dicing equipment to interlock Spindle load profile on sawing process control with data logging capability.

### 8.0 REFERENCES

1. Mohs Hardness Scale

2. Step Cut Kerf Delta Report, 2022 EPTC Symposium, Singapore.

3. KnS Silicon Carbide Dicing Report

4. Disco Blade Seminar, Engineering R&D Department

5. Dicing Thin wafers, Disco Japan.

6. Silicon Backside Chipping Analysis, SJSU, San Jose USA.

7. Sato, K., Yamada, T., & Nishikawa, T. (2017). Advanced Dicing Techniques for SiC Power Devices. Journal of Semiconductor Manufacturing, 25(3), 45–50.

8. Yoshimura, M., Fujimoto, K., & Yamabe, S. (2020). Evaluation of Blade Performance for Hard Substrate Dicing. Proceedings of the International Symposium on Semiconductor Process Technology, 14(1), 101–106.

9. Kuroda, H., Suzuki, Y., & Nakagawa, R. (2019). Self-Dressing Metal Bond Blades for Efficient Dicing of SiC Wafers. Materials Science in Semiconductor Processing,

10. Kato, A. & Inoue, S. (2021). Single-Pass Dicing of SiC Using Optimized Metal Bond Blades.

### 9.0 ABOUT THE AUTHORS

## **34<sup>th</sup> ASEMEP National Technical Symposium**

Eli Q. Novenario is a graduate of BS Electrical Engineering at Adamson University in Malate, Manila. He has 24 years of experience in the field of Semiconductor Assembly Manufacturing. He is currently working as Chief Process Engineer in Pre-Assembly, Ampleon Philippines. Prior this technical report, He authored a paper entitled, Z1 and Z2 Kerf Delta, a key parameter for top chipping control presented to EPTC symposium in Singapore.

Rex T. Dao-ayan received his bachelor's degree in Electronics Engineering from Saint Louis University, Baguio City. He specializes in the dicing process which includes Taiko and GaN wafer sawing. Rex is a Senior Process Sawing Engineer at Ampleon, where he leads a team of technicians in the wafer dicing process and System Automation.

Rodel B. Palad is a graduate of BS Mechanical Engineering from Saint Louis University Baguio City. He has been with Ampleon Phil. Inc. since 2015 and is currently assigned as Manufacturing Quality Engineer of Wafer Test and Pre-Assembly process lines.